# Area efficient SR flip-flop designed using 90nm CMOS technology

# Akshay Malhotra<sup>1\*</sup> and Rajesh Mehra<sup>2</sup>

ME Scholar, Department of Electronics & Communication Engineering, National Institute of Technical Teachers Training & Research, Chandigarh, India<sup>1</sup>

Associate Professor, Department of Electronics & Communication Engineering, National Institute of Technical Teachers Training & Research, Chandigarh, UT, India<sup>2</sup>

©2018 ACCENTS

## Abstract

In this paper SR flip-flop is designed to reduce area and power using 90nm technology for efficient utilization of the circuit. This is done using digital schematic (DSCH) and microwind application. Two designs have been proposed for SR flip-flop, namely fully automatic and semicustom design. In fully automatic design inbuilt active devices are used along with auto routing and placements. In semi-custom design inbuilt active devices are used with optimized manual routing and placement. The proposed schematic in case of fully automatic approach is designed by using DSCH and its equivalent layout is created using microwind. While in the case of semi-custom approach optimized layout is created with microwind. It can be observed from the simulated results that power is reduced by 81% and area consumption is improved by 15% in case of semi-custom design as compared to fully automatic design.

## **Keywords**

Area, CMOS FET, Layout, Power, Sequential circuits, SR flip-flop.

# **1.Introduction**

The primary objective of this S-R flip-flop design is to reduce the area so that the circuit fits into the integrated circuit chip efficiently. required Secondarily, this paper also aims to reduce the power consumed by the circuit for efficient utilization of power provided to the integrated circuit chip. Sequential circuits are circuits in which output is determined by current inputs as well as past inputs and thus they require memory. The combinational circuit does not use any memory. Hence the previous state of input does not have any effect on the present state of the circuit. Sequential circuits have memory so output can vary based on given input. These type of circuits use previous input, output, clock and a memory element. Sequential circuit designs use flipflops or latches, which are sometimes called memory elements that hold data. Sequential circuits are sorted as bistable, mono stable and astable. Bistable states have two stable states, either of them can be attained as per given conditions. Among the group of sequential circuits, the bistable circuits are the most popular ones. Timing elements such as latches, flipflops, registers, and memory storage cells form the group of most important components in synchronous VLSI designs [1-2].

221

Very-large-scale integration (VLSI) is the procedure of making an integrated circuit (IC) by integrating many transistors into a single chip. All basic elements like flip-flops, registers and memory elements fall in this category [3]. Before the introduction of VLSI technology, ICs could perform limited set of functions. ICs have advantage of speed, size and power consumption over digital circuits. We have number of different IC fabrication technologies. The most important difference between technologies is the types of transistors they can produce [4]. MOSFETs offer the advantage of drawing almost zero control current while idle [5]. They come in two variants: pMOS and nMOS using n-type and p-type dopants respectively. An individual complementary metal-oxide-semiconductor (CMOS) transistor consumes very little energy each time it switches on; the huge amount of transistors switching at very high speed rate makes power utilization a major design consideration [6-10]. In this paper the estimation of SR flip-flop's performance is done based on area measured.

Section 2 discusses the SR flip-flop. Section 3 shows design schematic simulations; layout analysis is done in section 4 followed by result comparison in section 5 and concluded in section 6.

<sup>\*</sup>Author for correspondence

Malhotra and Mehra

# 2.SR flip-flop

The SR latch or SR flip-flop can be considered as a basic sequential logic circuit. This simple flip-flop is a one-bit memory bistable device that has two inputs, one which will "SET" the device (meaning the output = "1"), and is labelled S and one which will "RESET" the device (meaning the output = "0"), labelled R. The SR stands for "Set-Reset". The reset input resets the flip-flop back to its original state with an output Q that will be either at a logic level "1" or logic "0" depending upon this set/reset condition [11,12].

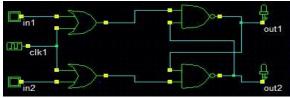

Figure 1 Clocked NAND based SR latch circuit

A basic NAND gate SR flip-flop circuit gives feedback through both its outputs back to its opposing inputs and is commonly used in memory circuits to store a single data bit [8]. Then the SR flip-flop actually has three inputs, Set, Reset and its current output Q related to its current state [6-7]. The word "Flip-flop" is related to the actual operation of the device, as it can be "flipped" into one logic Set state or "flopped" back to the opposing logic Reset state. The NAND based SR latch is implemented by combining the clock input as shown in *Figure 1*. The inputs (S and R) and clock signal (Clk1) are active low. It would mean that input signal will be nullified if clock is equal to logic '1' and those inputs will affect the outputs only when clock is active [13].

# **3.Schematic design simulation**

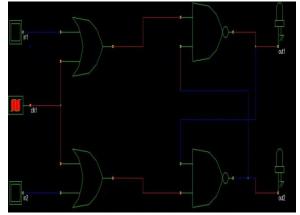

After designing the initial schematic circuit in *Figure 1*, we test the running of this circuit in DSCH for further analysis. This testing is depicted in *Figure 2*.

Figure 2 Simulation of NAND based sr latch circuit

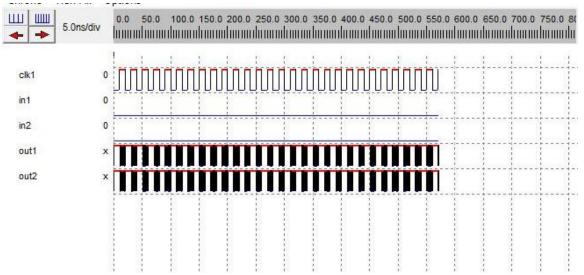

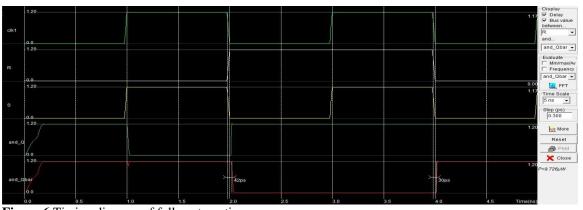

Further, then we study the timing diagram of the circuit in DSCH and compare it with ideal circuit timing diagram. This generated timing diagram is shown in *Figure 3*.

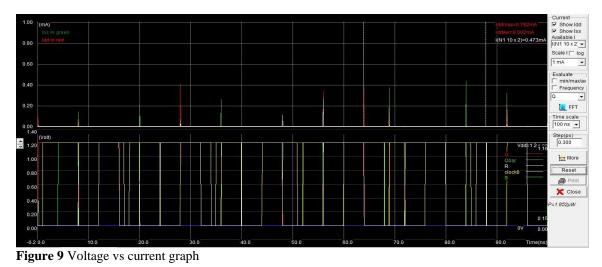

*Table 1* shows the theoretical truth table of SR flipflop. In microwind, we simulate the file generated from the DSCH and get the voltage vs current graph for the circuit. This graph is shown in *Figure 4*.

Figure 3 Timing diagram of fully automatic

| CLK                                     | S | R | QN | $ar{\mathbf{Q}}_{\mathbf{N+1}}$ | Operation                                                                           |  |  |

|-----------------------------------------|---|---|----|---------------------------------|-------------------------------------------------------------------------------------|--|--|

| 0                                       | 0 | 0 | 0  | 0                               | Not allowed                                                                         |  |  |

| 0                                       | 0 | 1 | 1  | 0                               | Set                                                                                 |  |  |

| 0                                       | 1 | 0 | 0  | 1                               | Reset                                                                               |  |  |

| 1                                       | Х | Х | Qn | Ōn                              | Hold                                                                                |  |  |

|                                         |   |   |    |                                 |                                                                                     |  |  |

| 1.00 (mA)<br>Iss in green<br>Idd in red |   |   |    |                                 | -Current<br>iddmax=0.077mA<br>iddAr=0.08mA<br>(V1.1 4 x2)=0.188mA<br>I(V1.1 4 x2) → |  |  |

| 0.60                                    |   |   |    |                                 | Scale I   T tog<br>1 mA v                                                           |  |  |

| 0.40                                    |   |   |    |                                 | Evaluate                                                                            |  |  |

| 0.20                                    |   |   |    |                                 | LUL, FFT                                                                            |  |  |

| 0.00                                    |   |   |    |                                 | Time scale                                                                          |  |  |

| 1.40<br>(Volt)<br>1.20                  |   |   |    |                                 | Vdd=1.2 ; ; ; ; 0.300                                                               |  |  |

| 1.00                                    | P |   |    |                                 | and_Obar                                                                            |  |  |

| 0.80                                    |   |   |    |                                 | Int Reset                                                                           |  |  |

|                                         |   |   |    |                                 | Close                                                                               |  |  |

| 0.40                                    |   |   |    |                                 | P=9.699µW                                                                           |  |  |

| Table 1  | S-R  | flip-flop | truth | table |

|----------|------|-----------|-------|-------|

| I abic I | 0 10 | mp nop    | uuun  | uuuu  |

Figure 4 Voltage vs current graph

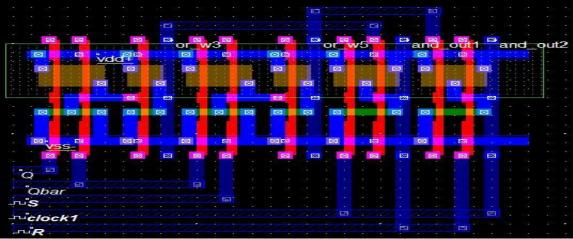

# 4.Layout design analysis

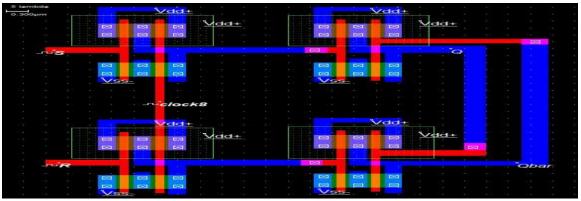

In the first method the schematic of SR flip-flop is designed, with the help of Microwind software the auto generated layout of SR flip-flop is created, afterwards simulation is done. In this, 90nm foundry is selected. The *Figure 5* represents the auto generated layout.

Figure 5 Fully automatic SR flip-flop

The layout is checked for DRC and if there no error is generated then simulated result appears. Later generated timing waveforms are verified by comparing to the circuit operation. The power generated is shown by the simulated result. The *Figure* 6 shows the timing diagram of this automatic layout. The power and area consumed by this layout is measured. Here the consuming power is 9.699  $\mu$ Watt. Area required for this particular layout is 65.2 $\mu$ m2 .Width is 8.8  $\mu$ m and height is 7.4  $\mu$ m. Secondly we prepare layout using semicustom approach. In semicustom approach the transistors are inbuilt, in this approach connections are made by following the lambda design rules. There is slight

Malhotra and Mehra

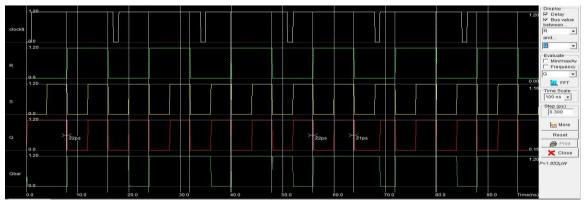

possibility of power reduction. *Figure 7* represents the layout using semicustom approach. The semicustom layout is checked for DRC if there is no error present in layout, the circuit is simulated and timing waveforms are generated. The generated timing waveforms are verified with the truth table or operation of original circuit.

Figure 8 shows the timing diagram of semicustom layout. The power observed from this particular

simulation, is 1.852  $\mu$ Watt, more than automatic layout and area is calculated from the properties. Here the width is 6.8  $\mu$ m (114 lambda) and height is 8.1  $\mu$ m (135 lambda). In semicustom layout area is 55.4  $\mu$ m<sup>2</sup>. Voltage versus current graph is shown in *Figure 9*.

Figure 6 Timing diagram of fully automatic

Figure 7 Semi custom SR flip-flop

Figure 8 Timing diagram of semi-custom layout

## International Journal of Advanced Technology and Engineering Exploration, Vol 5(44)

**5.Result comparison** The performance of proposed semi-custom layout is compared with automated layout. The performance parameters being area and power.

Through above results a comparative study can be done between the two designing approaches.

Comparative analysis table (*Table 2*) shows that in terms of power the performance of semi-custom layout approach decreases. In terms of area and power both the semi-custom layout has better performance among the two design approaches.

Table 2 Comparison table

| S. No. | Approach        | Area(µM <sup>2</sup> ) | Power(µWATT) |  |  |  |  |

|--------|-----------------|------------------------|--------------|--|--|--|--|

| 1.     | Fully Automatic | 65.2 μm <sup>2</sup>   | 9.699 μWatt  |  |  |  |  |

| 2.     | Semi-custom     | $55.4 \mu m^2$         | 1.852 µWatt  |  |  |  |  |

From the above comparison we observed, there is a reduction of 81% in power for semicustom layout generated in comparison to fully automatic layout and reduction of 15% in terms of area consumed. More area is required in auto generated approach. Comparative analysis in terms of area is done, which indicates that semi customized layouts have less area than auto generated [14, 15].

# **6.**Conclusion

From the above result analysis it is clear that semi customized layout is better than auto generated layout by 7.847  $\mu$ W in terms of power and 9.8  $\mu$ m2 better in terms of area consumption. So this design approach can be implemented where power reduction is the main consideration. The future scope is to try designing the circuit as fully custom design in microwind and hence work on reducing its power consumption and area to make it work efficiently in the integrated chip. To compare the efficiency of fully custom design with these two design approaches and work on getting better results through fully custom design approach.

## Acknowledgment

I would like to thank our honourable Director Dr. S.S. Pattnaik, National Institute of Technical Teachers Training & Research, Chandigarh, India for constant motivation, cooperation and support in pursuing my research work in ME Regular Program.

## **Conflicts of interest**

The authors have no conflicts of interest to declare.

## References

- Kaphungkui NK. Design of low-power, high performance flip-flops. International Journal of Applied Sciences and Engineering Research. 2014; 3(4):899-906.

- [2] Ziabakhsh S, Zoghi M. Design of a low-power highspeed t-flip-flop using the gate-diffusion input technique. In telecommunications forum TELFOR 2009 (pp. 1470-3).

- [3] Leblebici Y. CMOS digital integrated circuits: analysis and design. McGraw-Hill

- [4] Saxena A, Shinghal D, Shinghal K, Mukherjee S. Design and implementation of adiabatic based low power logic circuits. International Research Journal of Engineering and Technology. 2015; 2(2):498-504.

Malhotra and Mehra

- [5] Raj P, Mehra R. Performance and analysis of T flip flop using 90nm CMOS technology. International Journal of Electrical and Electronics Engineers. 2015; 7(1): 192-8.

- [6] Anjana S, Mehra R. Design and implementation of SR flip flop for efficient power using 90nm CMOS technology. International Journal of Scientific Research Engineering and Technology. 2015; 4(5):480-3.

- [7] Pinki, Mehra R. Design of low power high performance JK flip-flop. EATHD conference proceeding 2015 (pp.1-4).

- [8] Rahi PK, Dewangan S, Yadav T, Haque Md M. Design simulation and preferences analysis of JK flip flop using various CMOS techniques. International Journal for Research in Emerging Science and Technology.2015; 2(5):169-72.

- [9] Weste NH, Harris D. CMOS VLSI design: a circuits and systems perspective. Pearson Education India; 2015.

- [10] Mano M. M, Kime, C. Logic and computer design fundamentals. Pearson; 2013.

- [11] Aggarwal D. Review of flip-flop. Journal of Basic Applied and Engineering Research. 2014; 1(10):4-19.

- [12] Wolf W. Modern VISI design. Second Edition. Prentice Hall;1994.

- [13] Gupta P, Mehra R. Low power design of SR flip-flop using 45nm technology. IOSR Journal of VLSI and Signal Processing. 2016; 6(2):54-7.

- [14] Kaur U, Mehra R. Low power CMOS counter using clock gated flip-flop. International Journal of Engineering and Advanced Technology. 2013; 2(4):796-8.

- [15] Rajasri K, Bharathi A, Manikandan M. Performance of flip-flop using 22nm CMOS technology. International Journal of Innovative Research in Computer and Communication Engineering. 2014; 2(8):5272-6.

Akshay Malhotra received his Bachelors of Technology degree in Electronics and Telecommunication Engineering from Chandigarh College of Engineering and Technology (PU), Chandigarh, India in 2017. He is pursuing Masters of Engineering degree in Electronics and Communication

Engineering from National Institute of Technical Teachers Training and Research, Panjab University, Chandigarh, India.

Email: malhotraaki3@gmail.com

**Dr. Rajesh Mehra** is presently Head of Electronics and Communication Engineering Department at National Institute of Technical Teachers Training & Research, Chandigarh, India. He has received his Doctor of Philosophy and Masters Degree in Electronics & Communication

Engineering from Punjab University, Chandigarh, India. Dr. Mehra has completed his Bachelor of Technology from NIT, Jalandhar, India. Dr. Mehra has 22 years of Academic Experience along with 10 years of research experience. He has nearly 500 publications in refereed peer reviewed international journals and international conferences. Dr. Mehra has guided more than 100 PG scholars for their ME thesis work and also guiding 03 independent PhD scholars in his research areas. His research areas include VLSI Design, Digital Signal & Image Processing, Renewable Energy and Energy Harvesting. He has authored one book on PLC & SCADA. Dr. Mehra is senior member of IEEE and Life member ISTE.